LAPORAN AKHIR 1

PERCOBAAN 1

1. Jurnal [kembali]

2. Alat dan Bahan [kembali]

Panel DL 2203C , Panel DL 2203D , Panel DL 2203S

Jumper

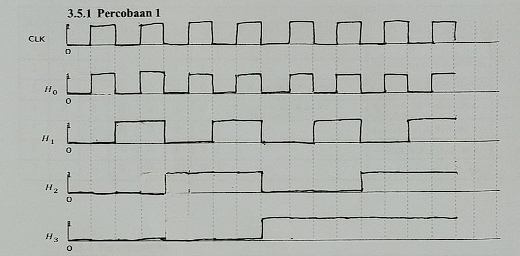

Pada percobaan 1, switch SPDT terhubung pada power, sehingga outputnya akan terbaca logic 1. Pada IC 74LS112 pada kaki RS-nya merupakan aktif LOW. Sehingga output yang dihasilkannya dipengaruhi oleh clock. Pada percobaan ini rangkaian ini terdiri dari 4 buah T flip-flop yang mana clock untuk flip-flop kedua, ketiga, dan keempat merupakan output dari Q FF sebelumnya.

Jadi rangkaian ini merupakan counter asynchronous karena pada rangkaian ini clocknya berjalan secara bertahap atau serial clock. Dan pin Set dan Reset dalam keadaan non aktif (kondisi tidak ada perubahan) dan T flip-flop berada dalam kondisi toggle karena JK bernilai 1.

Counter ini dapat menghitung bit dari 0 sampai 15, untuk mereset nilai Bit kita dapat mengaktifkan PIN reset dengan memberikan tegangan rendah atau di groundkan dan kita dapat menSet agar output bernilai 1 dengan cara mengaktifkan pin Set. Pada JK flip flop saat J=1 dan K=1 flip flop berada dalam kondisi toggle(keadaan berlawanan). setiap terjadi trigger output yang baru merupakan invers dari output yang lama.

5. Video Percobaan [kembali]

6. Analisa [kembali]

1. Analisa apa yang terjadi pada rangkaian percobaan 1 ketika input SR nya dihubungkan ke ground ketika SR aktif low ?

Jawab:

Jika SR pada JK Flip Flop dihubungkan ke ground maka inputan pada SR akan berlogika 0 yang mana Flip Flop akan aktif karena pada JK FF pada inputan SR terdapat tanda aktif ketika inputan LOW. Maka ketika aktif low, output tergantung pada inputan yang S atau R atau SR, jika dia dalam kondisi s maka ic akan meenunjukkan nilai terbesar dari logicnya sedangkan R dia akan menunjukkan nilai terkecil pada inputan, dan jika SR maka IC akan off

2. Apa yang terjadi jika output Q bar masing" flip flop dihubungkan ke input clock flip flop selanjutnya ?

Jawab:

Ketika Q bar dihubungkan ke clock maka output yang akan dibaca adalah kebalikan dari iputan dari Q, dikarenakan adanya delay pada output jk ff selanjutnya akan berbeda dari nilai pertaman namun karna adanya delay tersebut makan rangkaian dapat digunakan sebagai counter asynchronous

7. Download File [kembali]

Komentar

Posting Komentar