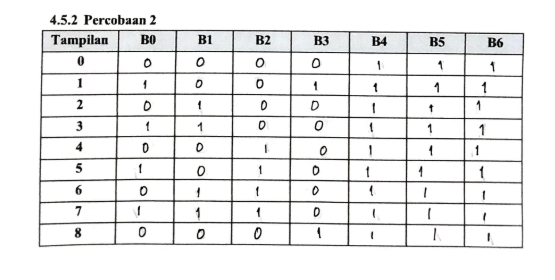

Laporan Akhir Modul 4 (Percobaan 1) [KEMBALI KE MENU SEBELUMNYA] DAFTAR ISI 1. Jurnal 2. Alat dan Bahan 3. Rangkaian Simulasi 4. Prinsip Kerja Rangkaian 5. Video Simulasi 6. Analisa 7. Link Download 1 . Jurnal [Kembali] 2. Alat dan Bahan [Kembali] Panel DL 2203C Panel DL 2203D Panel DL 2203S Jumper Gambar 1.1 Module D'Lorenzo Gambar 1.2 Jumper 3. Rangkaian Simulasi [Kembali] 4. Prinsip Kerja Rangkaian [Kembali] Pada percobaan 1 ini adalah rangkaian Serial in- serial out, Serial in-paralel out, paralel in- serial out, paralel in-paralel out shift register dengan kapasitas 4 bit, dirangkaian ini menggunakan 4 buah J-K flip flop yang terhubung denga 7 buah switch, Pada Flip Flop 1, kaki S terhubung ke B6', kaki J terhubung ke Q flip flop kedua, kaki K terhubung ke Q' flip flop kedua, kaki C terhubung ke output gerbang AND, kaki R terhubung ke B0, dan kaki Q terhu...